Dispositivos Lógicos Programáveis

Dispositivos Lógicos Programáveis

Linguagem VHDL

A linguagem VHDL (Very high speed integraded circuits (VHSIC) Hardware Description Language) permite descrever na forma de uma linguagem textual circuitos lógicos.

A linguagem VHDL pode ser utilizada para programar Dispositivos Lógicos Programáveis.

- Linguagem VHDL x Linguagem de Programação

- Uma linguagem de descrição de hardware descreve a configuração de hardware de um circuito, ao passo que uma linguagem de programação descreve uma sequência de instruções a serem executadas por um computador para realizar um tarefa.

- A execução de um programa em um computador segue uma ordem sequencial, por exemplo, caso o programa precise analisar o estado de quatro entradas, ele deve analisar uma entrada de de cada vez, a passo que um circuito lógico considera a atuação das entradas em paralelo [1] (p. 85).

Sintaxe VHDL

O formato de uma descrição de hardware envolve dois elementos fundamentais [1] (p. 88):

- Definição das entradas e saídas (bloco ENTITY);

- Definição de como as saídas respondem as entradas (bloco ARCHITECTURE).

Exemplo de uma porta AND:

ENTITY and_gate IS

PORT(

A, B : IN BIT;

S : OUT BIT);

END and_gate;

ARCHITECTURE ckr OF and_gate IS

BEGIN

S <= A AND B;

END ckt;

- Sinais intermediários

- São nós internos de um circuito lógico. São utilizados no VHDL para definir entradas e saídas de um bloco de circuito [1] (p. 90).

Exemplo de um circuito lógico dado pela expressão lógica:

S = AB + C

ENTITY logic_circuit IS

PORT(

A, B, C : IN BIT;

S : OUT BIT);

END logic_circuit;

ARCHITECTURE ckr OF logic_circuit IS

SIGNAL m :BIT;

BEGIN

m <= A AND B;

S <= m OR C;

END ckt;

Dados em VHDL

Dados numéricos representados em binário, hexadecimal e decimal [1] (p. 148):

B"11001" --Binário

X"19" --Hexadecimal

25 --Decimal

- Vetores de bits

- Exemplo porta p definida como uma entrada de 8 bits:

PORT(p :IN BIT_VECTOR(7 DOWNTO 0);

- Tipos de dados em VHDL

| Tipo de dados | Declaração | Valores possíveis | uso |

| BIT | y: OUT BIT; | '0', '1' | y <= '0' |

| BIT_VECTOR | bcd: OUT BIT_VECTOR (3 DOWNTO 0); | '0101', '1001', '0000' | bcd <= '0000'; |

| STD_LOGIC | y: OUT STD_LOGIC; | '0', '1', 'x', 'z' | y <= 'z' |

| STD_LOGIC_VECTOR | dbus: OUT STD_LOGIC_VECTOR (3 DOWNTO 0); | '0z1x' | dbus <= 'zzzz'; |

| INTEGER | SIGNAL z:INTERGER_RANGE 0 TO 31; | 0,1,2,...,31 | z <= 31; |

Tipos de dados:

- '0' -> Logico 0

- '1' -> Logico 1

- 'z' -> Alta Impedância

- 'x' -> Desconhecido

Circuitos lógicos construídos a partir da tabela verdade

Uma tabela verdade permite expressar o funcionamento de um circuito lógico combinacional.

Exemplo de uma porta AND descrita como tabela verdade em VHDL [1] (p. 152):

ENTITY and IS

PORT(

a,b: IN BIT;

s: OUT BIT);

END and;

ARCHITECTURE tabelaVerdade OF and IS

SIGNAL in_bits: BIT_VECTOR (1 DOWNTO 0);

BEGIN

in_bits <= a & b; --concatena bits

WITH in_bits SELECT

S <= '0' WHEN "00",

'0' WHEN "01",

'0' WHEN "10",

'1' WHEN "11";

END tabelaVerdade;

Estruturas de Controle em VHDL

A linguagem VHDL possui estruturas de controle de decisão que são interpretadas de forma sequencial, como numa linguagem de programação.

- IF/THEN/ELSE

- Exemplo de uso de IF/THEN/ELSE para comparar uma entrada inteira de 4 bits[1] (p. 157):

ENTITY teste IS

PORT(

valor_digital: IN INTEGER RANGE 0 TO 15; --entrada de 4 bits

z: OUT BIT);

END teste;

ARCHITECTURE desisao OF teste IS

BEGIN

PROCESS (valor_digital)

BEGIN

IF (valor_digital > 6) THEN

z <= '1';

ELSE

z <= '0';

END IF;

END PROCESS;

END desisao;

- IF/THEN/ELSEIF/THEN/ELSE

- Permite construir IFs aninhados.

- CASE

- Estrutura que permite percorrer uma lista de possíveis valores a serem avaliados[1] (p. 159).

ENTITY caso IS

PORT(

p,q,r: IN BIT;

s: OUT BIT);

END caso;

ARCHITECTURE copia OF caso IS

SIGNAL status: BIT_VECTOR (2 DOWNTO 0);

BEGIN

status <= p & q & r; --concatena bits

PROCESS (status)

BEGIN

CASE status IS

WHEN "100" => s <= '0';

WHEN "101" => s <= '0';

WHEN "110" => s <= '0';

WHEN OTHERS => s <= '1';

END CASE;

END PROCESS;

END copia;

Flip-Flops e Latchs em VHDL

O Quartus possui blocos primitivos de biblioteca para flip-flops e latchs [1] (p. 230-235).

Estes componentes possuem as portas de entrada e saída com identificação padrão no bloco primitivo, conforme a tabela:

| Função da porta | Identificação |

| Clock | clk |

| Preset assíncrono | prn |

| Clear assíncrono | clr |

| Entradas J, K, S, R, D | j, k, r, s, d |

| Saída Q | q |

- Latch D em VHDL

LIBRARY ieee;

USE ieee.std_logic_1164.all;

LIBRARY work;

ENTITY latchD IS

PORT

(

D : IN STD_LOGIC;

Clock : IN STD_LOGIC;

Qlatch : OUT STD_LOGIC

);

END latchD;

ARCHITECTURE bdf_type OF latchD IS

BEGIN

PROCESS(Clock,D)

BEGIN

IF (Clock = '1') THEN

Qlatch <= D;

END IF;

END PROCESS;

END bdf_type;

- Flip-flop D em VHDL

LIBRARY ieee;

USE ieee.std_logic_1164.all;

LIBRARY work;

ENTITY flipflopD IS

PORT

(

D : IN STD_LOGIC;

Clock : IN STD_LOGIC;

Qff : OUT STD_LOGIC

);

END flipflopD;

ARCHITECTURE bdf_type OF flipflopD IS

BEGIN

PROCESS(Clock)

BEGIN

IF (RISING_EDGE(Clock)) THEN

Qff <= D;

END IF;

END PROCESS;

END bdf_type;

Dispositivos Lógicos Programáveis

Um Dispositivo Lógico Programável (PLD) pode ser configurado eletronicamente para formar um circuito lógico. Normalmente são construídos como uma matriz de comutação com chaves que podem ser programadas [1] (p. 143).

A programação de um PLD utiliza software de desenvolvimento, com o qual o programador define como o dispositivo deve ser programado.

A descrição de um circuito lógico em um software de desenvolvimento pode ser realizada de diferentes maneiras, incluindo:

- Captura Esquemática;

- Expressão Lógica;

- Tabela Verdade;

- Linguagem VHDL.

O QUARTUS II é um software de desenvolvimento da Altera, com o qual é possível descrever um diagrama lógico como uma arquivo de descrição de bloco (.bdf) ou utilizando a linguagem VDHL (.vhd).

Quartus II

Software para desenvolvimento de circuitos lógicos digitais.

Instalação do Quartus II Web Edition no Linux

- Acessar Download Center Altera:

- Selecionar Quartus Prime software Lite edition - FREE, no license file required

- Selecionar versão 13.osp1: Quartus II Web Edition

- Versão compatível com MAX7000S

- Selecionar Individual Files:

- Quartus II Web Edition (Free):

- Quartus II Software

- ModelSim-Altera Edition

- Devices:

- MAX II, MAX V, MAX 3000, MAX 7000

- Additional Software:

- Quartus II Help

- Quartus II Web Edition (Free):

- Executar arquivos .run para instalação do software

Teste e possíveis erros

- Testar o Quartus

/opt/altera/13.0sp1/quartus/bin/quartus &

- Testar o ModelSim

/opt/altera/13.0sp1/modelsim_ase/bin/vsim &

- Possível ERRO 1

/opt/altera/13.0sp1/modelsim_ae/bin/vsim ** Fatal: Read failure in vlm process (0,0) Falha de segmentação (imagem do núcleo gravada)

- Isto ocorre porque várias ferramentas usadas pelo Quartus são 32 bits, para solucionar:

- Obtenha os arquivos abaixo e os armazene em uma pasta do Quartus com o nome lib32.

libfreetype.so libfreetype.so.6 libfreetype.so.6.10.2

- Estes arquivos podem ser obtidos através da biblioteca freetype2.

- Definir uma variável em /etc/bash.bashrc:

export LD_LIBRARY_PATH=/opt/altera/13.0sp1/lib32

- Instalar suporte para compactação bzip2 utilizado pelo Quartus 32 bits:

sudo apt-get install bzip2:i386

- Possível ERRO 2

$ vsim Error: cannot find "/opt/altera/13.0sp1/modelsim_ase/bin/../linux_rh60/vsim"

- Solução

- edite o arquivo vco na linha 206, diretório /opt/altera/13.0sp1/modelsim_ase/

*) vco="linux_rh60" ;;

- para

*) vco="linux" ;;

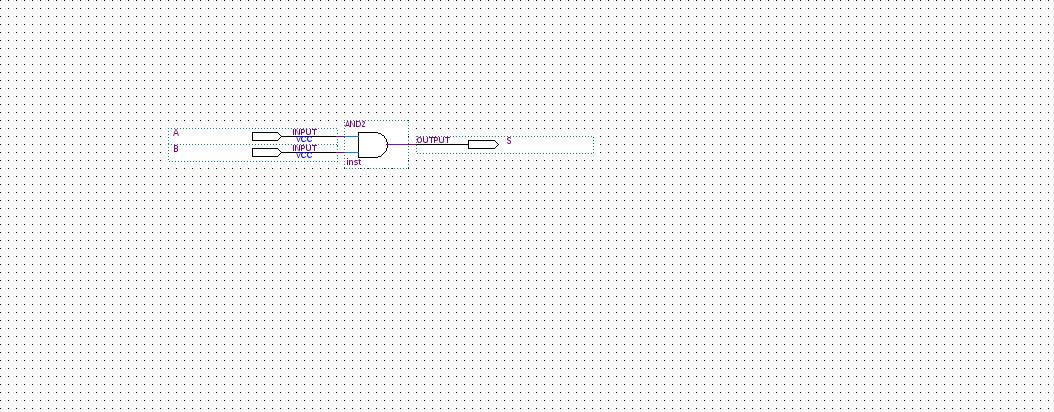

Exemplo de utilização do Quartus II

- Circuito de uma porta E constuída no Quartus II

- Block Diagram/Schematic File

- VHDL de uma porta E gerada pelo Quartus II

-- PROGRAM "Quartus II 32-bit"

-- VERSION "Version 13.0.1 Build 232 06/12/2013 Service Pack 1 SJ Full Version"

-- CREATED "Fri May 12 15:17:16 2017"

LIBRARY ieee;

USE ieee.std_logic_1164.all;

LIBRARY work;

ENTITY portaE IS

PORT(

A : IN STD_LOGIC;

B : IN STD_LOGIC;

S : OUT STD_LOGIC);

END portaE;

ARCHITECTURE bdf_type OF portaE IS

BEGIN

S <= A AND B;

END bdf_type;

Referências

--Evandro.cantu (discussão) 14h03min de 12 de maio de 2017 (BRT)