Dispositivos Lógicos Programáveis

De Wiki Cursos IFPR Foz

Dispositivos Lógicos Programáveis

Linguagem VHDL

A linguagem VHDL (Very high speed integraded circuits (VHSIC) Hardware Description Language) permite descrever na forma de uma linguagem textual circuitos lógicos.

A linguagem VHDL pode ser utilizada para programar Dispositivos Lógicos Programáveis.

- Linguagem VHDL x Linguagem de Programação

- Uma linguagem de descrição de hardware descreve a configuração de hardware de um circuito, ao passo que uma linguagem de programação descreve uma sequência de instruções a serem executadas por um computador para realizar um tarefa.

- A execução de um programa em um computador segue uma ordem sequencial, por exemplo, caso o programa precise analisar o estado de quatro entradas, ele deve analisar uma entrada de de cada vez, a passo que um circuito lógico considera a atuação das entradas em paralelo [1] (p. 85).

Sintaxe VHDL

O formato de uma descrição de hardware envolve dois elementos fundamentais [1] (p. 88):

- Definição das entradas e saídas (bloco ENTITY);

- Definição de como as saídas respondem as entradas (bloco ARCHITECTURE).

Exemplo de uma porta AND:

ENTITY and_gate IS

PORT(

A : IN BIT;

B : IN BIT);

END and_gate;

ARCHITECTURE ckr OF and_gate IS

BEGIN

S <= A AND B;

END ckt;

- Sinais intermediários

- São nós internos de um circuito lógico. São utilizados no VHDL para definir entradas e saídas de um bloco de circuito.

Quartus II

Software para desenvolvimento de circuitos lógicos digitais.

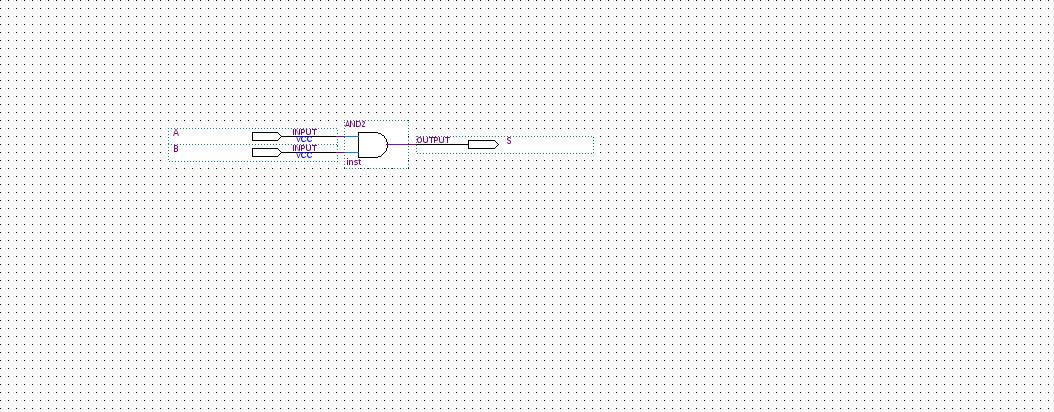

- Circuito de uma porta E constuida no Quartus II

- Block Diagram/Schematic File

- VHDL de uma porta E gerada pelo Quartus II

-- PROGRAM "Quartus II 32-bit"

-- VERSION "Version 13.0.1 Build 232 06/12/2013 Service Pack 1 SJ Full Version"

-- CREATED "Fri May 12 15:17:16 2017"

LIBRARY ieee;

USE ieee.std_logic_1164.all;

LIBRARY work;

ENTITY portaE IS

PORT(

A : IN STD_LOGIC;

B : IN STD_LOGIC;

S : OUT STD_LOGIC);

END portaE;

ARCHITECTURE bdf_type OF portaE IS

BEGIN

S <= A AND B;

END bdf_type;

- Porta E construída a partir da tabela verdade

ENTITY e IS

PORT(

a,b: IN BIT;

s: OUT BIT);

END e;

ARCHITECTURE tabelaVerdade OF e IS

SIGNAL in_bits: BIT_VECTOR (1 DOWNTO 0);

BEGIN

in_bits <= a & b;

WITH in_bits SELECT

S <= '0' WHEN "00",

'0' WHEN "01",

'0' WHEN "10",

'1' WHEN "11";

END tabelaVerdade;

Referências

--Evandro.cantu (discussão) 14h03min de 12 de maio de 2017 (BRT)