Latch SR com portas NAND

Latch SR com portas NAND

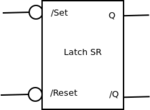

Este é um dos mais simples circuitos de flip-flop, construído com portas NAND. Note na figura que, além das entradas, as saídas das portas NAND realimentam o circuito, dando a ele a característica de memória.

As saídas do circuito são denominadas Q e /Q, e em condições normais, são sempre uma o inverso da outra.

O latch SR possui duas entradas: a entrada /Set que seta a saída Q para 1 e a entrada /Reset que reseta a saída Q para 0.

As entradas /Set e /Reset devem estar normalmente em estado ALTO (1), somente quando se deseja setar ou resetar a saída do latch, uma delas é pulsada ao estado BAIXO (0). Por serem ativo baixo, representamos estas entradas com a barra de negação.

- Análise das saídas do latch SR com portas NAND

- Verifique que quando /Set=/Reset=1 há dois estados de saída possíveis e estáveis, tanto com Q=0 e /Q=1, como com Q=1 e /Q=0.

- Quando /Set=0 e /Reset=1 o latch é setado, fazendo com que Q=1 e /Q=0.

- Quando /Set=1 e /Reset=0 o latch é resetado, fazendo com que Q=0 e /Q=1.

- As entradas /Set=/Reset=0, simultaneamente, são proibidas.

- Verifique que, uma vez setado (ou resetado) o latch, ele mantém os dados armazenados na saída enquanto /Set=/Reset=1.

- Exercícios

- Sobre o latch SR com portas NAND

- Para a análise das saídas do latch SR, construa desenhos com os diversos estados possíveis para as entradas e saídas;

- Construa a tabela verdade do latch SR;

--Evandro.cantu (discussão) 10h51min de 12 de junho de 2014 (BRT)

Referências

TOCCI, R.J.; WIDMER, N.S.; MOSS, G.L. Sistemas Digitais: princípios e aplicações, São Paulo: Pearson, 2011.

- Autoria

- Evandro Cantú / IFPR - Câmpus Foz do Iguaçu