Dispositivos Lógicos Programáveis: mudanças entre as edições

| Linha 57: | Linha 57: | ||

<syntaxhighlight lang="vhdl"> | <syntaxhighlight lang="vhdl"> | ||

PORT(p :IN BIT_VECTOR(7 DOWNTO 0); | PORT(p :IN BIT_VECTOR(7 DOWNTO 0); | ||

</syntaxhighlight> | |||

===Circuitos lógicos construídos a partir da tabela verdade=== | |||

Uma '''tabela verdade''' permite expressar o funcionamento de um '''circuito lógico combinacional'''. | |||

Exemplo de uma '''porta AND''' descrita como '''tabela verdade''' em '''VHDL''': | |||

<syntaxhighlight lang="vhdl"> | |||

ENTITY and IS | |||

PORT( | |||

a,b: IN BIT; | |||

s: OUT BIT); | |||

END and; | |||

ARCHITECTURE tabelaVerdade OF e IS | |||

SIGNAL in_bits: BIT_VECTOR (1 DOWNTO 0); | |||

BEGIN | |||

in_bits <= a & b; | |||

WITH in_bits SELECT | |||

S <= '0' WHEN "00", | |||

'0' WHEN "01", | |||

'0' WHEN "10", | |||

'1' WHEN "11"; | |||

END tabelaVerdade; | |||

</syntaxhighlight> | </syntaxhighlight> | ||

| Linha 98: | Linha 121: | ||

S <= A AND B; | S <= A AND B; | ||

END bdf_type; | END bdf_type; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

Edição das 21h59min de 17 de maio de 2017

Dispositivos Lógicos Programáveis

Linguagem VHDL

A linguagem VHDL (Very high speed integraded circuits (VHSIC) Hardware Description Language) permite descrever na forma de uma linguagem textual circuitos lógicos.

A linguagem VHDL pode ser utilizada para programar Dispositivos Lógicos Programáveis.

- Linguagem VHDL x Linguagem de Programação

- Uma linguagem de descrição de hardware descreve a configuração de hardware de um circuito, ao passo que uma linguagem de programação descreve uma sequência de instruções a serem executadas por um computador para realizar um tarefa.

- A execução de um programa em um computador segue uma ordem sequencial, por exemplo, caso o programa precise analisar o estado de quatro entradas, ele deve analisar uma entrada de de cada vez, a passo que um circuito lógico considera a atuação das entradas em paralelo [1] (p. 85).

Sintaxe VHDL

O formato de uma descrição de hardware envolve dois elementos fundamentais [1] (p. 88):

- Definição das entradas e saídas (bloco ENTITY);

- Definição de como as saídas respondem as entradas (bloco ARCHITECTURE).

Exemplo de uma porta AND:

ENTITY and_gate IS

PORT(

A, B : IN BIT;

S : OUT BIT);

END and_gate;

ARCHITECTURE ckr OF and_gate IS

BEGIN

S <= A AND B;

END ckt;

- Sinais intermediários

- São nós internos de um circuito lógico. São utilizados no VHDL para definir entradas e saídas de um bloco de circuito [1] (p. 90).

Exemplo de um circuito lógico pela expressão lógica:

S = AB + C

ENTITY logic_circuit IS

PORT(

A, B, C : IN BIT;

S : OUT BIT);

END logic_circuit;

ARCHITECTURE ckr OF logic_circuit IS

SIGNAL m :BIT;

BEGIN

m <= A AND B;

S <= m OR C;

END ckt;

Dados em VHDL

Dados numéricos representados em binário, hexadecimal e decimal [1] (p. 148):

B"11001" --Binário

X"19" --Hexadecimal

25 --Decimal

- Vetores de bits

- Exemplo porta p definida como uma entrada de 8 bits:

PORT(p :IN BIT_VECTOR(7 DOWNTO 0);

Circuitos lógicos construídos a partir da tabela verdade

Uma tabela verdade permite expressar o funcionamento de um circuito lógico combinacional.

Exemplo de uma porta AND descrita como tabela verdade em VHDL:

ENTITY and IS

PORT(

a,b: IN BIT;

s: OUT BIT);

END and;

ARCHITECTURE tabelaVerdade OF e IS

SIGNAL in_bits: BIT_VECTOR (1 DOWNTO 0);

BEGIN

in_bits <= a & b;

WITH in_bits SELECT

S <= '0' WHEN "00",

'0' WHEN "01",

'0' WHEN "10",

'1' WHEN "11";

END tabelaVerdade;

Dispositivos Lógicos Programáveis

Um Dispositivo Lógico Programável (PLD) pode ser configurado eletronicamente para formar um circuito lógico. Normalmente são construídos como uma matriz de comutação com chaves que podem ser programadas [1] (p. 143).

A programação de um PLD utiliza software de desenvolvimento, com o qual o programador define como o dispositivo deve ser programado.

A descrição de um circuito lógico em um software de desenvolvimento pode ser realizada de diferentes maneiras, incluindo:

- Captura Esquemática;

- Expressão Lógica;

- Tabela Verdade;

- Linguagem VHDL.

O QUARTUS II é um software de desenvolvimento da Altera, com o qual é possível descrever um diagrama lógico como uma arquivo de descrição de bloco (.bdf) ou utilizando a linguagem VDHL (.vhd).

Quartus II

Software para desenvolvimento de circuitos lógicos digitais.

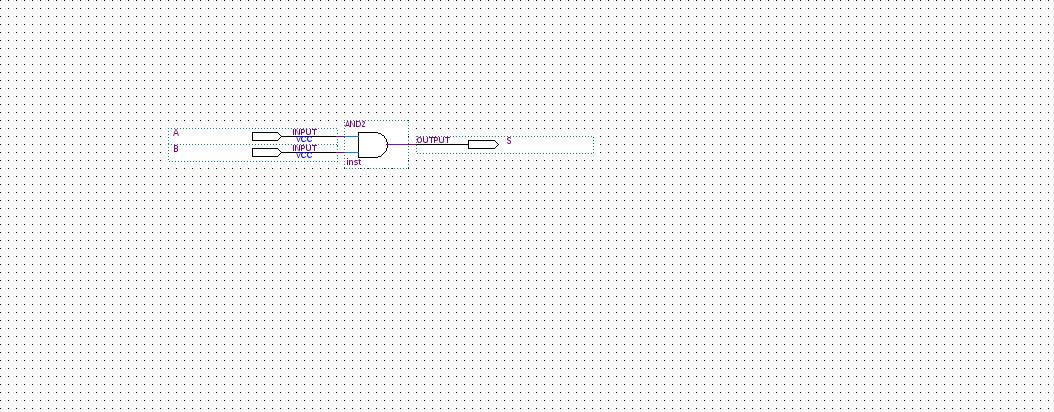

- Circuito de uma porta E constuida no Quartus II

- Block Diagram/Schematic File

- VHDL de uma porta E gerada pelo Quartus II

-- PROGRAM "Quartus II 32-bit"

-- VERSION "Version 13.0.1 Build 232 06/12/2013 Service Pack 1 SJ Full Version"

-- CREATED "Fri May 12 15:17:16 2017"

LIBRARY ieee;

USE ieee.std_logic_1164.all;

LIBRARY work;

ENTITY portaE IS

PORT(

A : IN STD_LOGIC;

B : IN STD_LOGIC;

S : OUT STD_LOGIC);

END portaE;

ARCHITECTURE bdf_type OF portaE IS

BEGIN

S <= A AND B;

END bdf_type;

Referências

--Evandro.cantu (discussão) 14h03min de 12 de maio de 2017 (BRT)