Dispositivos Lógicos Programáveis: mudanças entre as edições

De Wiki Cursos IFPR Foz

Ir para navegaçãoIr para pesquisar

| Linha 3: | Linha 3: | ||

==Linguagem VHDL== | ==Linguagem VHDL== | ||

A linguagem '''VHDL''' ('' | A linguagem '''VHDL''' (''Hardware Description Language'') permite descrever na forma de uma linguagem textual '''circuitos lógicos'''. | ||

Pode ser utilizada para | Pode ser utilizada para programar '''Dispositivos Lógicos Programáveis'''. | ||

==Quartus II== | ==Quartus II== | ||

Edição das 12h54min de 15 de maio de 2017

Dispositivos Lógicos Programáveis

Linguagem VHDL

A linguagem VHDL (Hardware Description Language) permite descrever na forma de uma linguagem textual circuitos lógicos.

Pode ser utilizada para programar Dispositivos Lógicos Programáveis.

Quartus II

Software para desenvolvimento de circuitos lógicos digitais.

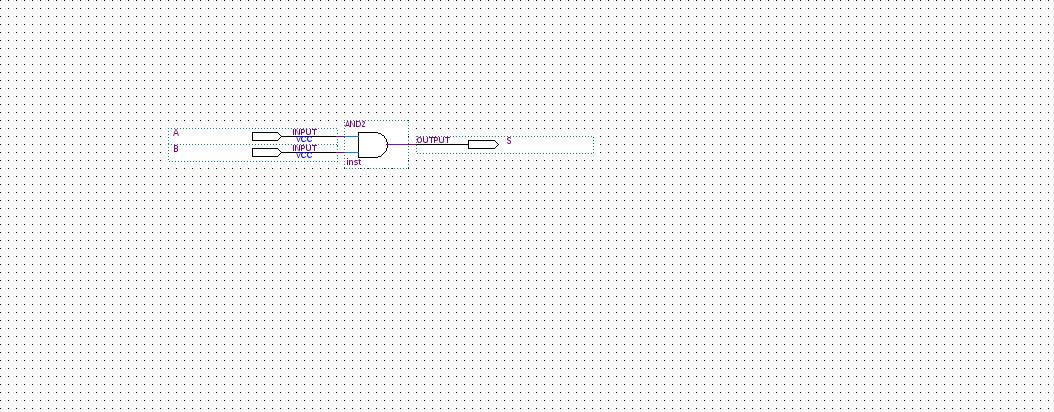

- Circuito de uma porta E constuida no Quartus II

- Block Diagram/Schematic File

- VHDL de uma porta E gerada pelo Quartus II

-- PROGRAM "Quartus II 32-bit"

-- VERSION "Version 13.0.1 Build 232 06/12/2013 Service Pack 1 SJ Full Version"

-- CREATED "Fri May 12 15:17:16 2017"

LIBRARY ieee;

USE ieee.std_logic_1164.all;

LIBRARY work;

ENTITY portaE IS

PORT(

A : IN STD_LOGIC;

B : IN STD_LOGIC;

S : OUT STD_LOGIC);

END portaE;

ARCHITECTURE bdf_type OF portaE IS

BEGIN

S <= A AND B;

END bdf_type;

- Porta E construída a partir da tabela verdade

ENTITY e IS

PORT(

a,b: IN BIT;

s: OUT BIT);

END e;

ARCHITECTURE tabelaVerdade OF e IS

SIGNAL in_bits: BIT_VECTOR (1 DOWNTO 0);

BEGIN

in_bits <= a & b;

WITH in_bits SELECT

S <= '0' WHEN "00",

'0' WHEN "01",

'0' WHEN "10",

'1' WHEN "11";

END tabelaVerdade;

--Evandro.cantu (discussão) 14h03min de 12 de maio de 2017 (BRT)