Flip-Flops: mudanças entre as edições

| (15 revisões intermediárias por 2 usuários não estão sendo mostradas) | |||

| Linha 1: | Linha 1: | ||

=Elementos de Memória e | =Flip-Flops e Elementos de Memória<ref name="TOCCI">TOCCI, R.J.; WIDMER, N.S.; MOSS, G.L. Sistemas Digitais: princípios e aplicações, São Paulo: Pearson, 2011.</ref>= | ||

'''Elementos de memória''' são circuitos que permitem armazenar valores para uso posterior. O elemento de memória mais elementar é o '''flip-flop''', o qual é comporto por um conjunto portas lógicas e é capaz de armazenar 1 bit. | '''Elementos de memória''' são circuitos que permitem armazenar valores para uso posterior. O elemento de memória mais elementar é o '''flip-flop''', o qual é comporto por um conjunto portas lógicas e é capaz de armazenar 1 bit. | ||

==Flip-flop SR com portas NOR== | |||

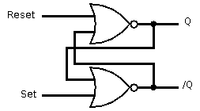

Este é um dos mais simples circuitos de '''flip-flop''', construído com portas NOR. Note na figura que, além das entradas, as saídas das portas NOR realimentam o circuito, dando a ele a característica de memória. O Flip-flop SR é comumente chamado de '''''Latch'' SR'''. | |||

Este é um dos mais simples circuitos de '''flip-flop''', construído com portas NOR. Note na figura que, além das entradas, as saídas das portas NOR realimentam o circuito, dando a ele a característica de memória. | |||

[[Arquivo:Flip-flopSR.png | 200px]] Símbolo:[[Arquivo:LatchSR-NOR.png | 150px]] | [[Arquivo:Flip-flopSR.png | 200px]] Símbolo:[[Arquivo:LatchSR-NOR.png | 150px]] | ||

| Linha 13: | Linha 11: | ||

;Características: | ;Características: | ||

*As saídas do circuito são denominadas '''Q''' e '''/Q''', e em condições normais, são sempre uma o inverso da outra. | *As saídas do circuito são denominadas '''Q''' e '''/Q''', e em condições normais, são sempre uma o inverso da outra. | ||

*O | *O flip-flop SR possui duas entradas: a entrada '''Set''' que seta a saída Q para 1 e a entrada '''Reset''' que reseta a saída Q para 0. | ||

*As entradas Set e Reset devem estar normalmente em estado BAIXO (0), somente quando se deseja setar ou resetar a saída do | *As entradas Set e Reset devem estar normalmente em estado BAIXO (0), somente quando se deseja setar ou resetar a saída do flip-flop, uma delas é pulsada ao estado ALTO (1). | ||

;Análise das saídas do | ;Análise das saídas do flip-flop SR com portas NOR | ||

*Verifique que quando Set=Reset=0 há dois estados de saída possíveis e estáveis, tanto com Q=0 e /Q=1, como com Q=1 e /Q=0. | *Verifique que quando Set=Reset=0 há dois estados de saída possíveis e estáveis, tanto com Q=0 e /Q=1, como com Q=1 e /Q=0. | ||

*Quando Set=1 e Reset=0 o latch é '''setado''', fazendo com que Q=1 e /Q=0. | *Quando Set=1 e Reset=0 o latch é '''setado''', fazendo com que Q=1 e /Q=0. | ||

| Linha 23: | Linha 21: | ||

*Verifique que, uma vez setado (ou resetado) o ''latch'', ele mantém os dados armazenados na saída enquanto Set=Reset=0. | *Verifique que, uma vez setado (ou resetado) o ''latch'', ele mantém os dados armazenados na saída enquanto Set=Reset=0. | ||

;Vídeo: [https://www.youtube.com/watch?v=8piKnuad73g | ;Vídeo: [https://www.youtube.com/watch?v=8piKnuad73g Flip-Flop SR portas NOR] | ||

;Exercícios: Sobre o | ;Exercícios: Sobre o flip-flop SR com portas NOR | ||

#Para a análise das saídas do | #Para a análise das saídas do flip-flop SR, construa desenhos com os diversos '''estados''' possíveis para as entradas e saídas; | ||

#Construa a '''tabela verdade''' do | #Construa a '''tabela verdade''' do flip-flop SR; | ||

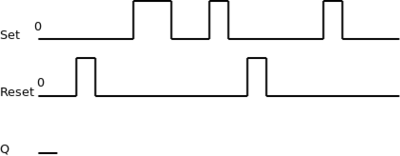

#Determine as '''formas de onda''' das saídas do | #Determine as '''formas de onda''' das saídas do flip-flop SR, considerando que as formas de onda mostradas na figura sejam aplicadas nas entradas. | ||

[[Arquivo:DiagramaTempo2.png | 400px]] | [[Arquivo:DiagramaTempo2.png | 400px]] | ||

; | ;Observação: O flip-flop SR também pode ser construído com portas NAND: [[Latch SR com portas NAND | Flip-flop SR com portas NAND]]. | ||

== | ==Circuitos Sequenciais ou Circuitos com Clock== | ||

'''Circuitos sequenciais''' são circuitos cujo nível lógico da(s) saída(s) depende da combinação dos níveis lógicos das entradas e também de elementos de memória. Além disto, os circuitos sequenciais geralmente operam de modo síncrono, cadenciados por sinais de relógio (ou pulsos de '''''clock'''''). Neste caso, os pulsos do ''clock'' determinam o momento em que as saídas podem mudar de estado. | |||

[[Clock | '''Sinais de Clock''']] | |||

[[ | |||

== Flip-flops com ''clock''== | == Flip-flops com ''clock''== | ||

| Linha 63: | Linha 51: | ||

{| border="1" cellpadding="2" style="text-align: center;" | {| border="1" cellpadding="2" style="text-align: center;" | ||

|- | |- | ||

| | | Set || Reset || CLK || Q<sub>n</sub> | ||

|- | |- | ||

| X || X || Sem CLK || Q<sub>n-1</sub> | | X || X || Sem CLK || Q<sub>n-1</sub> | ||

|- | |- | ||

| | | 0 || 0 || ^ || Q<sub>n-1</sub> | ||

|- | |- | ||

| | | 1 || 0 || ^ || 1 | ||

|- | |- | ||

| | | 0 || 1|| ^ || 0 | ||

|- | |- | ||

| | | 1 || 1 || ^ || Proibido | ||

|} | |} | ||

Obs: | Obs: | ||

| Linha 124: | Linha 112: | ||

===Exercícios=== | ===Exercícios=== | ||

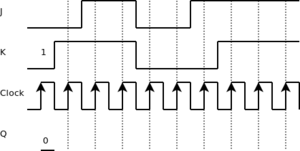

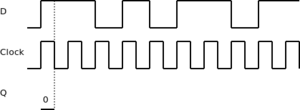

1) Determine as formas de onda das saídas do '''flip-flop JK com ''clock'' disparado pela borda de subida''', considerando que as formas de onda mostradas na figura sejam aplicadas nas entradas: | |||

[[Arquivo:Flip-flopJK.png | 200px]] Diagrama de tempo: [[Arquivo:DiagramaTempo4.png | 300px]] | |||

[[Arquivo:Flip-flopJK.png | 200px]] | |||

[[Arquivo:Flip-flopD2.png | 200px]] Diagrama de tempo: [[Arquivo:DiagramaTempo5.png | 300px]] | |||

Diagrama de tempo: | |||

[[Arquivo:DiagramaTempo4.png | 300px]] | |||

2) Determine as formas de onda das saídas do '''flip-flop D com ''clock'' disparado pela borda de descida''', considerando que as formas de onda mostradas na figura sejam aplicadas nas entradas: | |||

[[Arquivo:Flip-flopD2.png | 200px]] | |||

Diagrama de tempo: | |||

[[Arquivo:DiagramaTempo5.png | 300px]] | |||

==Laboratório e Exercícios de Simulação== | |||

;Para este laboratório será utilizado o [[Simulador de Circuitos Lógicos - Logisim]]:Veja no ''link'' as instruções para ''download'' e instalação do programa. | |||

===Flip-flops=== | |||

#Construir e simular o circuito do Latch SR, construído com portas NOR, conforme a figura: [[Arquivo:Flip-flopSR.png | 200px]] | |||

#*Construa a tabela verdade; | |||

#Simule o funcionamento do Latch SR presente no Logisim e compare sua tabela verdade com o circuito do Latch SR construído com portas NOR. | |||

#Simule o funcionamento do Flip-flop JK presente no Logisim. | |||

#Simule o funcionamento do Flip-flop D presente no Logisim. | |||

==Referências== | ==Referências== | ||

<references /> | |||

---- | ---- | ||

--[[Usuário:Evandro.cantu|Evandro.cantu]] ([[Usuário Discussão:Evandro.cantu|discussão]]) 10h48min de 12 de junho de 2014 (BRT) | |||

---- | ---- | ||

[[Categoria:Sistemas Digitais]] | [[Categoria:Sistemas Digitais]] | ||

Edição atual tal como às 17h44min de 12 de junho de 2019

Flip-Flops e Elementos de Memória[1]

Elementos de memória são circuitos que permitem armazenar valores para uso posterior. O elemento de memória mais elementar é o flip-flop, o qual é comporto por um conjunto portas lógicas e é capaz de armazenar 1 bit.

Flip-flop SR com portas NOR

Este é um dos mais simples circuitos de flip-flop, construído com portas NOR. Note na figura que, além das entradas, as saídas das portas NOR realimentam o circuito, dando a ele a característica de memória. O Flip-flop SR é comumente chamado de Latch SR.

- Características

- As saídas do circuito são denominadas Q e /Q, e em condições normais, são sempre uma o inverso da outra.

- O flip-flop SR possui duas entradas: a entrada Set que seta a saída Q para 1 e a entrada Reset que reseta a saída Q para 0.

- As entradas Set e Reset devem estar normalmente em estado BAIXO (0), somente quando se deseja setar ou resetar a saída do flip-flop, uma delas é pulsada ao estado ALTO (1).

- Análise das saídas do flip-flop SR com portas NOR

- Verifique que quando Set=Reset=0 há dois estados de saída possíveis e estáveis, tanto com Q=0 e /Q=1, como com Q=1 e /Q=0.

- Quando Set=1 e Reset=0 o latch é setado, fazendo com que Q=1 e /Q=0.

- Quando Set=0 e Reset=1 o latch é resetado, fazendo com que Q=0 e /Q=1.

- As entradas Set=Reset=1, simultaneamente, são proibidas.

- Verifique que, uma vez setado (ou resetado) o latch, ele mantém os dados armazenados na saída enquanto Set=Reset=0.

- Vídeo

- Flip-Flop SR portas NOR

- Exercícios

- Sobre o flip-flop SR com portas NOR

- Para a análise das saídas do flip-flop SR, construa desenhos com os diversos estados possíveis para as entradas e saídas;

- Construa a tabela verdade do flip-flop SR;

- Determine as formas de onda das saídas do flip-flop SR, considerando que as formas de onda mostradas na figura sejam aplicadas nas entradas.

- Observação

- O flip-flop SR também pode ser construído com portas NAND: Flip-flop SR com portas NAND.

Circuitos Sequenciais ou Circuitos com Clock

Circuitos sequenciais são circuitos cujo nível lógico da(s) saída(s) depende da combinação dos níveis lógicos das entradas e também de elementos de memória. Além disto, os circuitos sequenciais geralmente operam de modo síncrono, cadenciados por sinais de relógio (ou pulsos de clock). Neste caso, os pulsos do clock determinam o momento em que as saídas podem mudar de estado.

Flip-flops com clock

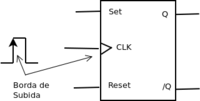

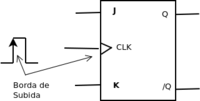

Cada flip-flop tem uma entrada de clock, a qual normalmente é disparada pela borda (positiva ou negativa).

Normalmente, chama-se de latch os flip-flop sem clock disparado pela borda. Quando há presença de clock para sincronismo disparado pela borda, chama-se de flip-flop.

Flip-flop SR

- Flip-flop SR com clock disparado pela borda de subida

Tabela verdade:

| Set | Reset | CLK | Qn |

| X | X | Sem CLK | Qn-1 |

| 0 | 0 | ^ | Qn-1 |

| 1 | 0 | ^ | 1 |

| 0 | 1 | ^ | 0 |

| 1 | 1 | ^ | Proibido |

Obs:

- ^:Indica borda de subida do clock;

- Qn : Estado atual da saída;

- Qn-1 : Estado anterior da saída (mantém estado).

- Exercício

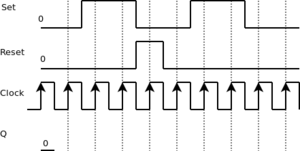

Determine as formas de onda das saídas do flip-flop SR com clock disparado pela borda de subida, considerando que as formas de onda mostradas na figura sejam aplicadas nas entradas:

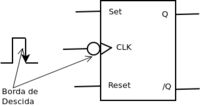

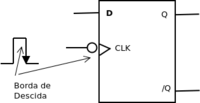

- Flip-flop SR com clock disparado pela borda de descida

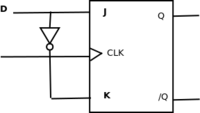

Flip-flop JK

- Flip-flop JK clock disparado pela borda de subida

- Há também flip-flop JK com clock disparado pela borda de descida

Tabela verdade:

| J | K | CLK | Qn |

| 0 | 0 | ^ | Qn-1 (mantém) |

| 1 | 0 | ^ | 1 |

| 0 | 1 | ^ | 0 |

| 1 | 1 | ^ | /Qn-1 (comuta) |

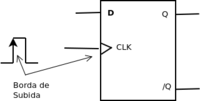

Flip-flop D

- Flip-flop D com clock disparado pela borda de subida

- Há também flip-flop D com clock disparado pela borda de descida

Tabela verdade:

| D | CLK | Qn |

| 0 | ^ | 0 |

| 1 | ^ | 1 |

Exercícios

1) Determine as formas de onda das saídas do flip-flop JK com clock disparado pela borda de subida, considerando que as formas de onda mostradas na figura sejam aplicadas nas entradas:

Diagrama de tempo:

2) Determine as formas de onda das saídas do flip-flop D com clock disparado pela borda de descida, considerando que as formas de onda mostradas na figura sejam aplicadas nas entradas:

Diagrama de tempo:

Laboratório e Exercícios de Simulação

- Para este laboratório será utilizado o Simulador de Circuitos Lógicos - Logisim

- Veja no link as instruções para download e instalação do programa.

Flip-flops

- Construir e simular o circuito do Latch SR, construído com portas NOR, conforme a figura:

- Construa a tabela verdade;

- Simule o funcionamento do Latch SR presente no Logisim e compare sua tabela verdade com o circuito do Latch SR construído com portas NOR.

- Simule o funcionamento do Flip-flop JK presente no Logisim.

- Simule o funcionamento do Flip-flop D presente no Logisim.

Referências

- ↑ TOCCI, R.J.; WIDMER, N.S.; MOSS, G.L. Sistemas Digitais: princípios e aplicações, São Paulo: Pearson, 2011.

--Evandro.cantu (discussão) 10h48min de 12 de junho de 2014 (BRT)